# Agilent E9522A **Freescale StarCore140 Nexus Decoder**

# **Design Guide**

# Notices

© Agilent Technologies, Inc. 2005. 2006

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

#### **Manual Part Number**

#### E9522-97001

This manual is available online at www.agilent.com. It is not an orderable part.

#### **Revision History**

E9522-97001, March 2006

Agilent Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### **Trademark Acknowledgements**

Windows and MS Windows are U.S. registered trademarks of Microsoft Corporation.

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June

1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

#### **Safety Notices**

# CAUTION

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

## WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

#### **1** Introduction

In This Guide... 5 Product Overview 5 **Target System Requirements** 6 Supported processor 6 **Object files** 6 Supported compilers 6 Connectors 6 **Equipment Required** 7 Logic analysis system 7 Logic analyzer cards 7 Table 1. Logic analyzer channels required 7 Probes 7

#### 2 Designing Your Board

**Overview of the Connectors** 9 Designing the Connectors 11 **AMP MICTOR 38 connectors** 11 Signal-To-Connector Mappings 12 J1: Nexus signals for Agilent logic analysis and ARM RealView Trace 12 J2: Upper Nexus signals for logic analysis 13 Bus and signal descriptions 13 Sharing the Connector Between Multiple Tools 15 **Option 1: Linked connectors** 15 Option 2: Two separate connectors 16 **Option 3: Splitter board** 17

Index

# In This Guide...

This *Design Guide* provides information to assist you in designing a board which will be compatible with the Agilent E9522A Freescale StarCore140 Nexus Decoder. It tells you what signals are required by the decoder, and suggests how to route these signals to a connector.

For information on using the decoder, see the online help which is installed with the decoder.

# **Product Overview**

The Freescale StarCore140 Nexus Decoder, used with an Agilent Technologies logic analyzer, allows you to decode and view messages from an SC140 DSP core in your target system.

The decoder can decode 2-, 4-, 8-, 16-, 30-, and 32-bit wide data. (The 30-bit width is to support decode of traces that are captured by the on-chip buffer and subsequently unloaded by a JTAG tool.)

# **Target System Requirements**

The decoder has been designed to work with target systems meeting the following requirements:

### Supported processor

• StarCore140 "Platform 2002"

#### **Object files**

• You must have access to the object files for the code which is executing on your target system.

### **Supported compilers**

• Metrowerks CodeWarrior IDE version 5.5.xxxx, or a compiler which generates object files with an equivalent ELF object file format.

## Connectors

• You must provide a connector, as described in this guide, to connect the logic analyzer probes to the signals on your target system.

# **Equipment Required**

## Logic analysis system

You need an Agilent 16900-series or 1680/90-series logic analyzer.

#### Logic analyzer cards

The logic analyzer card(s) you use must support the speed of the bus you are probing.

The logic analyzer card(s) must provide enough channels to probe the connectors on your target system.

| Probing scheme             | Number of connectors | Number of logic<br>analyzer channels<br>required | Number of<br>68-cannel logic<br>analyzer cards |

|----------------------------|----------------------|--------------------------------------------------|------------------------------------------------|

| 2, 4, 8, or 16 MDO signals | 1                    | 32                                               | 1                                              |

| 30 or 32 MDO signals       | 2                    | 64                                               | 1                                              |

| <b>T</b> I I <b>A</b> |                 |          |          |

|-----------------------|-----------------|----------|----------|

| Table 1               | I odie analyzor | channele | roduirod |

| ιανις ι               | Logic analyzer  | CHAINERS | reuureu  |

|                       |                 |          |          |

#### Probes

You need an appropriate number of logic analyzer probes ("adapter cables") to connect the logic analyzer cables to the connectors on your target system. The probe must match the type of connector you have placed on your board. Agilent recommends a MICTOR connector and an Agilent E5346A or E5380A probe.

#### **1** Introduction

# **Designing Your Board**

This chapter describes the factors you need to consider when designing and preparing your target system for logic analysis.

## **Overview of the Connectors**

#### **Recommended connectors**

Agilent recommends that you provide one or two AMP MICTOR 38 connectors with the signal mappings shown in the following sections. Use connector J1 if you have 16 or fewer data lines. Use connectors J1 and J2 if you have more than 16 data lines.

You may also need to provide a 2x10 berg connector for JTAG-only signals. See "Sharing the Connector Between Multiple Tools" on page 15 for more information on this connector.

#### **Alternative connectors**

You are free to use any connector or pin routing, as long as you provide all of the logic analyzer signals that are described for the recommended connectors.

If you use a connector or a signal-to-pin mapping other than what is described in this chapter, the Agilent-supplied configuration file will not work. You will need to create your own logic analyzer configuration file. Extreme care must be taken to ensure that your configuration file meets the requirements of the decoder.

• Use a provided configuration file as a model.

- Make sure that your configuration file has the same buses and signals as the provided configuration file. The name and size of each bus and signal must be *exactly* the same as it is in the provided configuration file.

- Verify that all buses and signals listed in the "Buses and signals captured by the logic analyzer" help topic are present.

- Verify that each bus and signal meets all of the requirements specified in this *Design Guide*.

## **Designing the Connectors**

# **AMP MICTOR 38 connectors**

The signal-to-connector mappings shown in this chapter assume you are using AMP MICTOR 38 connectors.

Each MICTOR 38 connector carries 32 signals plus two clocks (CLK1 for two logic analyzer pods). Probes (part number E5346A, sometimes called "high-density termination cables") are required to connect the logic analyzer cables to the MICTOR connector. These probes contain the required termination. One probe is required for every two logic analyzer pods.

To increase the structural support for the probes, you should use support shrouds on each connector.

For more information, including mechanical dimensions, see the Agilent Technologies E5346A 38-Pin Probe and E5351A 38-Pin Adapter Cable Installation Note, available from www.agilent.com.

#### **Design Considerations**

The connector must be close enough to the signal source so that the stub length created is less than  $^{1}\!/_{5}$  the  $t_{r}$  (bus risetime). For PC board material, (er = 4.9) and  $Z_{o}$  in the range of 50 - 80 $\Omega$ , use a propagation delay of 160 ps/inch of stub.

Each probed signal line must be able to supply a minimum of 600 mV to the probe tip and handle a minimum of 90 k $\Omega$  shunted by 10 pF. The maximum input voltage to the logic analyzer is  $\pm 40$ V peak

# **Signal-To-Connector Mappings**

## J1: Nexus signals for Agilent logic analysis and ARM RealView Trace

J1 is designed to be used either with an Agilent logic analyzer *or* with ARM's RealView Trace. When J1 is used with the logic analyzer, the JTAG (run control) signals (shaded in blue) must be routed to a separate JTAG-only connector (page 15) so they are accessible to a JTAG controller such as ARM RealView ICE.

The signals shaded in blue are used by RealView Trace, but are not used by the logic analyzer.

| Analyzer Pod | Nexus Signal | Mictor pin #<br>Nexus Signal (top view) |    | Nexus Signal  | Analyzer Pod |

|--------------|--------------|-----------------------------------------|----|---------------|--------------|

| 5V           | NC           | 1                                       | 2  | NC            | 120          |

| 5V           | NC           | 3                                       | 4  | NC            | 12C          |

| CLK even     | NC-pulldown  | 5                                       | 6  | МСКО          | CLK odd      |

| D15 even     | DBGRQ        | 7                                       | 8  | MRDY or DBACK | D15 odd      |

| D14 even     | nSRST        | 9                                       | 10 | EVTI          | D14 odd      |

| D13 even     | TDO          | 11                                      | 12 | VTRef         | D13 odd      |

| D12 even     | RTCLK        | 13                                      | 14 | VSupply       | D12 odd      |

| D11 even     | TCK          | 15                                      | 16 | MD07          | D11 odd      |

| D10 even     | TMS          | 17                                      | 18 | MD06          | D10 odd      |

| D9 even      | TDI          | 19                                      | 20 | MD05          | D9 odd       |

| D8 even      | nTRST        | 21                                      | 22 | MD04          | D8 odd       |

| D7 even      | MD015        | 23                                      | 24 | MD03          | D7 odd       |

| D6 even      | MD014        | 25                                      | 26 | MD02          | D6 odd       |

| D5 even      | MD013        | 27                                      | 28 | MD01          | D5 odd       |

| D4 even      | MD012        | 29                                      | 30 | NC-pulldown   | D4 odd       |

| D3 even      | MD011        | 31                                      | 32 | EVTO          | D3 odd       |

| D2 even      | MD010        | 33                                      | 34 | MSE0 1        | D2 odd       |

| D1 even      | MD09         | 35                                      | 36 | MSEO 0        | D1 odd       |

| D0 even      | MD08         | 37                                      | 38 | MDO 0         | D0 odd       |

## J2: Upper Nexus signals for logic analysis

This connector is required only if the Nexus core is set up to collect more than 16 bits of data.

| Analyzer Pod | Nexus Signal | Mictor pin #<br>(top view) |    | Nexus Signal | Analyzer Pod |

|--------------|--------------|----------------------------|----|--------------|--------------|

| 5V           | NC           | 1                          | 2  | NC           | 12C          |

| 5V           | NC           | 3                          | 4  | NC           | 12C          |

| CLK even     | NC           | 5                          | 6  | NC           | CLK odd      |

| D15 even     | MD031        | 7                          | 8  | NC           | D15 odd      |

| D14 even     | MD030        | 9                          | 10 | NC           | D14 odd      |

| D13 even     | MD029        | 11                         | 12 | NC           | D13 odd      |

| D12 even     | MD028        | 13                         | 14 | NC           | D12 odd      |

| D11 even     | MD027        | 15                         | 16 | NC           | D11 odd      |

| D10 even     | MD026        | 17                         | 18 | NC           | D10 odd      |

| D9 even      | MD025        | 19                         | 20 | NC           | D9 odd       |

| D8 even      | MD024        | 21                         | 22 | NC           | D8 odd       |

| D7 even      | MD023        | 23                         | 24 | NC           | D7 odd       |

| D6 even      | MD022        | 25                         | 26 | NC           | D6 odd       |

| D5 even      | MD021        | 27                         | 28 | NC           | D5 odd       |

| D4 even      | MD020        | 29                         | 30 | NC           | D4 odd       |

| D3 even      | MD019        | 31                         | 32 | NC           | D3 odd       |

| D2 even      | MD018        | 33                         | 34 | NC           | D2 odd       |

| D1 even      | MD017        | 35                         | 36 | NC           | D1 odd       |

| D0 even      | MD016        | 37                         | 38 | NC           | D0 odd       |

|              |              |                            |    |              |              |

## **Bus and signal descriptions**

- **MD0** Required. Data lines. This bus may be 2, 4, 8, 16, 30, or 32 bits wide.

- **MSE0** Required. Start or End of Message. This bus may be 1 or 2 bits wide.

- **EVT0** Required. A value of 1 on this signal indicates that a trigger event has occurred. 1 bit wide.

#### **2 Designing Your Board**

- **NC** Pins 1, 2, 3, and 4 must be true no-connects. Other NC signals can be left floating (no connects), or used to measure other signals of interest.

- **Other signals** Optional. **The decoder ignores the signals shaded in blue.** These signals are routed to the connector to allow the connector to be used by a JTAG controller such as ARM's RealView ICE. See the documentation for your JTAG controller for information on the requirements for these signals.

These signals must be routed to a second, JTAG-only connector so that they are accessible to the JTAG controller. See "Sharing the Connector Between Multiple Tools" on page 15 for a description of the second connector.

In addition, special consideration must be given to these signals so that the logic analyzer does not load them, such that they cannot be controlled by the JTAG controller. Use a 10 k $\Omega$  pullup resistor to avoid such loading. See the *Agilent Technologies E5346A 38-Pin Probe and E5351A 38-Pin Adapter Cable Installation Note* for information on how the probe loads the signals.

## Sharing the Connector Between Multiple Tools

The standard connector defined in this document is designed to be used with a JTAG controller (JTAG run-control and trace) or a logic analyzer (trace only).

There are three possible ways to provide these signals to RealView ICE and at the same time, prevent the logic analyzer from interfering with their use.

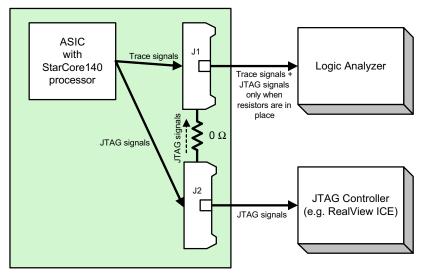

### **Option 1: Linked connectors**

Route the JTAG signals to two connectors on the board. Daisy-chain the signals first to a JTAG-only 2X10 berg connector (J2), then to the MICTOR connector (J1). Place zero-Ohm resistors between the two connectors. Leave the zero-Ohm resistors in place when using J1 with RealView Trace. Remove the resistors when using J1 with the logic analyzer.

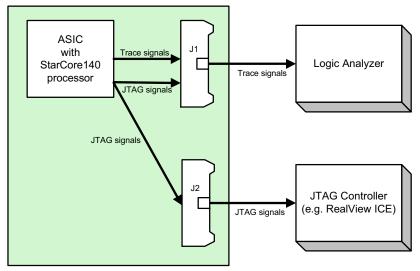

## **Option 2: Two separate connectors**

Route the JTAG signals to two connectors in a star configuration. Provide 10 k $\Omega$  pull-up resistors on the signals (particularly nSRST) so that the logic analyzer does not pull these signals to ground.

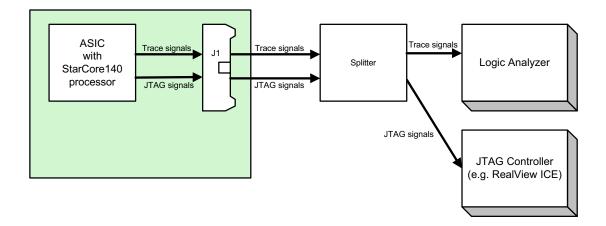

## **Option 3: Splitter board**

Route the JTAG signals to one MICTOR connector (J1) and use a splitter board such as Agilent product number E9595A Option 002 to provide the JTAG-only connector for RealView ICE.

2 Designing Your Board

# Index

# C

compilers, 6 connectors, 11

## E

E9595A, 17 equipment required, 7

### Η

headers, 11

# L

logic analyzer cards number required, 7

## Μ

MICTOR connectors, 11

#### Ρ

probes number required, 7 processors supported, 5

## R

RealView Trace, 15

## S

splitter board, 17

Index